授权公布号:CN107507637B

一种低功耗双列直插式存储器及其增强驱动方法

有效

申请

2017-09-18

申请公布

2017-12-22

授权

2024-02-27

预估到期

2037-09-18

| 申请号 | CN201710841231.9 |

| 申请日 | 2017-09-18 |

| 申请公布号 | CN107507637A |

| 申请公布日 | 2017-12-22 |

| 授权公布号 | CN107507637B |

| 授权公告日 | 2024-02-27 |

| 分类号 | G11C5/02;G11C5/14;G11C11/4074;G11C7/12N;G11C7/18N;G11C8/08N;G11C8/14N;G11C11/408N;G11C11/409N |

| 分类 | 信息存储; |

| 申请人名称 | 深圳市江波龙电子股份有限公司 |

| 申请人地址 | 广东省深圳市南山区科发路8号金融服务技术创新基地1栋8楼A、B、C、D、E、F1 |

专利法律状态

2024-02-27

授权

状态信息

授权

2018-11-27

著录事项变更

状态信息

著录事项变更;IPC(主分类):G11C5/02;变更事项:申请人;变更前:深圳市江波龙电子有限公司;变更后:深圳市江波龙电子股份有限公司;变更事项:地址;变更前:518057 广东省深圳市南山区科发路8号金融基地1栋8楼;变更后:518000 广东省深圳市南山区科发路8号金融服务技术创新基地1栋8楼A、B、C、D、E、F1

2018-01-19

实质审查的生效

状态信息

实质审查的生效;IPC(主分类):G11C5/02;申请日:20170918

2017-12-22

公布

状态信息

公布

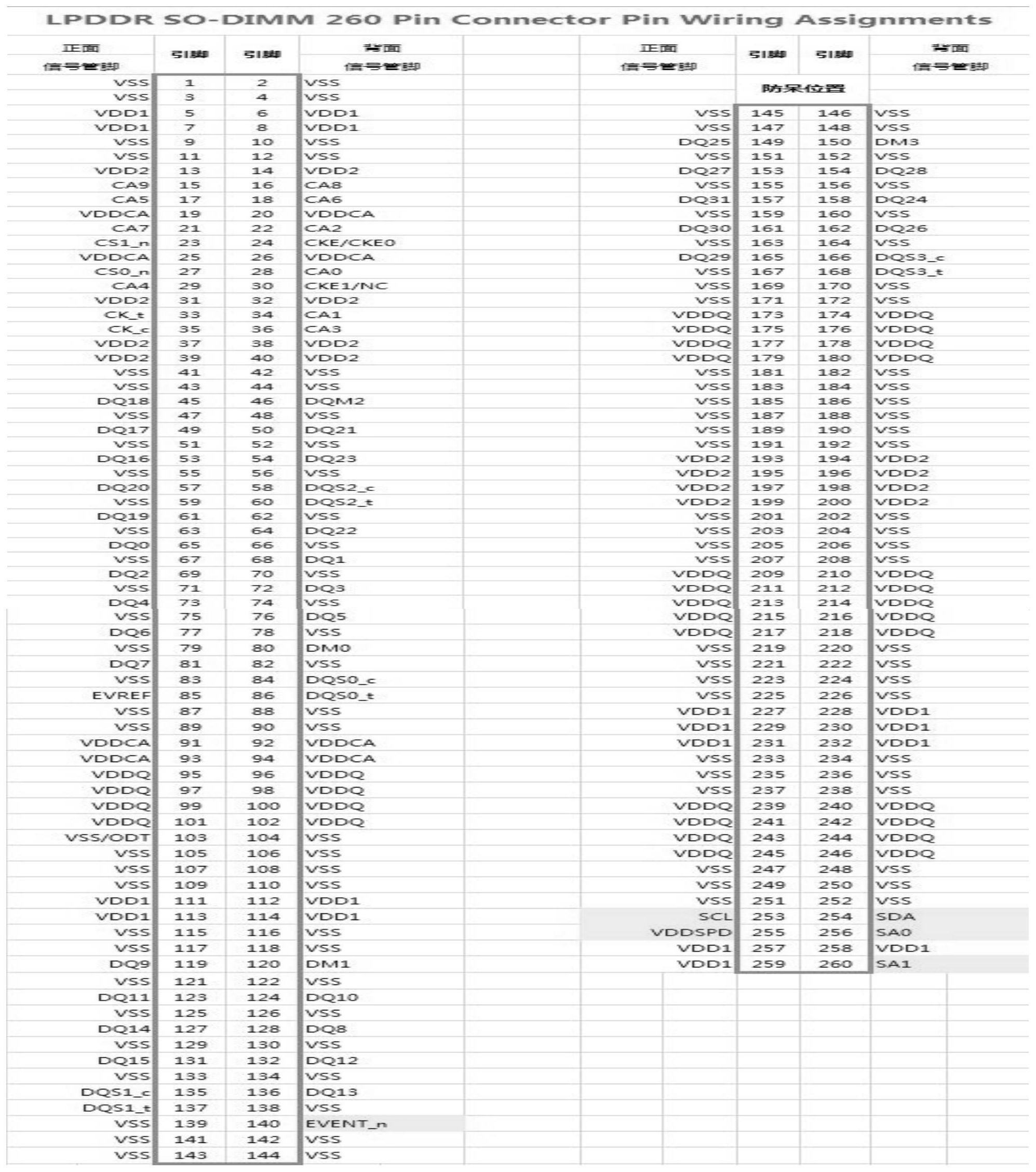

摘要

本发明适用于电子领域,提供了一种低功耗双列直插式存储器及其增强驱动方法,该存储器为可插拔双列直插式结构,兼容DDR内存接口,存储器基于低功耗内存芯片的DDR4 SO‑DIMM接口以信号完整性和电源完整性为原则做如下引脚分配:存储器的电源引脚和接地引脚通过对DDR4 SO‑DIMM接口的数据线、控制线和地址线的两端从新分配得到,使布线时数据线、控制线、地址线通过电源引脚和接地引脚隔离;存储器的电源引脚和接地引脚按一定的比例进行分配。本发明利用了现有的笔记本内存接口规格DDR4 SO‑DIMM,将LPDDR2/3/4定义在此接口规范上,实现低功耗、大容量以及即插即用的需求。