授权公布号:CN114584246B

基于FPGA的无线自组网时间同步方法、系统及介质

有效

申请

2022-03-01

申请公布

2022-06-03

授权

2023-08-15

预估到期

2042-03-01

| 申请号 | CN202210197185.4 |

| 申请日 | 2022-03-01 |

| 申请公布号 | CN114584246A |

| 申请公布日 | 2022-06-03 |

| 授权公布号 | CN114584246B |

| 授权公告日 | 2023-08-15 |

| 分类号 | H04J3/06;H04W56/00;H04W84/18;H04L1/1607 |

| 分类 | 电通信技术; |

| 申请人名称 | 四川九洲电器集团有限责任公司 |

| 申请人地址 | 四川省绵阳市科创园区九华路6号 |

专利法律状态

2023-08-15

授权

状态信息

授权

2022-06-21

实质审查的生效

状态信息

实质审查的生效;IPC(主分类):H04J3/06;申请日:20220301

2022-06-03

公布

状态信息

公布

摘要

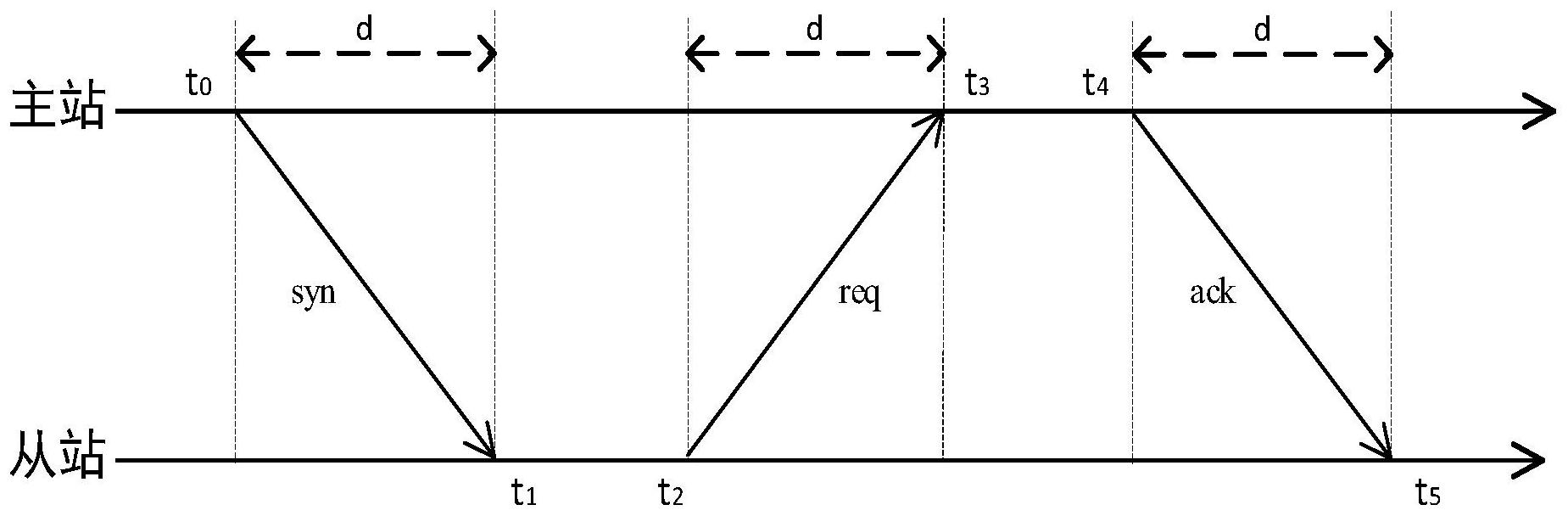

本发明公开了基于FPGA的无线自组网时间同步方法、系统及介质,涉及无线通信技术领域,其技术方案要点是:主站节点发送包含当前时间t0的syn时间帧;当从站节点接收到syn时间帧后,从syn时间帧中提取当前时间t0对从站节点的时间进行更新;从站节点发送包含当前时间t2的req时间帧;主站节点收到req时间帧后记录本节点的当前时间t3;主站节点发送包含当前时间t4和t3的ack时间帧;当从站节点收到ack时间帧后记录本节点当前时间t5,依据当前时间t2、t3、t4和t5计算得到传输时延,并进行时间补偿。本发明通过设计时间帧协议,节点之间的时间同步只需交互各自的时间信息,以减少时间同步的网络开销。