授权公布号:CN112017105B

颜色校正FPGA实现装置和方法、颜色校正设备和存储介质

有效

申请

2020-08-13

申请公布

2020-12-01

授权

2024-03-26

预估到期

2040-08-13

| 申请号 | CN202010810265.3 |

| 申请日 | 2020-08-13 |

| 申请公布号 | CN112017105A |

| 申请公布日 | 2020-12-01 |

| 授权公布号 | CN112017105B |

| 授权公告日 | 2024-03-26 |

| 分类号 | G06T1/20;G06T7/90;H04N23/10;H04N25/10 |

| 分类 | 计算;推算;计数; |

| 申请人名称 | 深圳市洲明科技股份有限公司 |

| 申请人地址 | 广东省深圳市宝安区福永街道桥头社区永福路112号A栋 |

专利法律状态

2024-03-26

授权

状态信息

授权

2020-12-01

公布

状态信息

公布

摘要

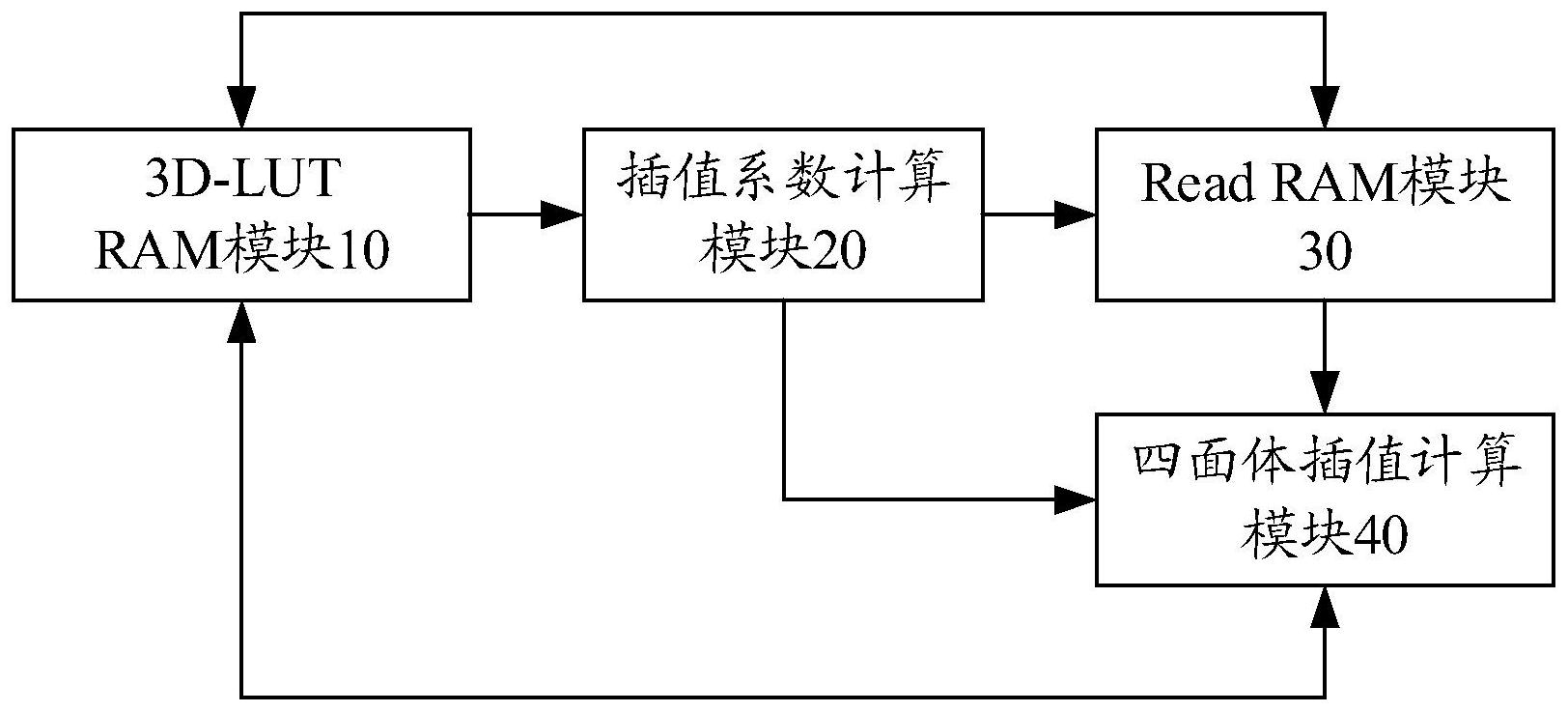

本发明公开了一种颜色校正FPGA实现装置和方法、颜色校正设备和存储介质,所述装置包括:3D‑LUT RAM模块、插值系数计算模块、Read RAM模块、四面体插值计算模块;其中:所述3D‑LUT RAM模块用于存储3D‑LUT采样数据;所述插值系数计算模块用于计算输入像素颜色在3D‑LUT色域的映射,计算出插值系数和参与插值的3D‑LUT颜色位置;所述Read RAM模块用于根据插值系数计算模块的输出参数选择插值顶点并转换成RAM的取值地址进行读取插值点数据;所述四面体插值计算模块用于根据Read RAM模块确定的RAM取值地址,从所述3D‑LUT RAM模块中取出3D‑LUT采样数据进行插值计算。通过本发明实施例,能够有效的简化插值公式的权值计算,无误差计算出小数部分,同时支持非(2n+1)个点的3D‑LUT采样数据,3D‑LUT采样数据支持色深到16bit。