授权公布号:CN108735708B

芯片结构、及其封装方法以及电子设备

有效

申请

2018-07-18

申请公布

2018-11-02

授权

2024-01-19

预估到期

2038-07-18

| 申请号 | CN201810792234.2 |

| 申请日 | 2018-07-18 |

| 申请公布号 | CN108735708A |

| 申请公布日 | 2018-11-02 |

| 授权公布号 | CN108735708B |

| 授权公告日 | 2024-01-19 |

| 分类号 | H01L23/498;H01L21/48 |

| 分类 | 基本电气元件; |

| 申请人名称 | 北京比特大陆科技有限公司 |

| 申请人地址 | 北京市海淀区奥北科技园25号楼2层 |

专利法律状态

2024-01-19

授权

状态信息

授权

2018-11-27

实质审查的生效

状态信息

实质审查的生效;IPC(主分类):H01L23/498;申请日:20180718

2018-11-02

公布

状态信息

公布

摘要

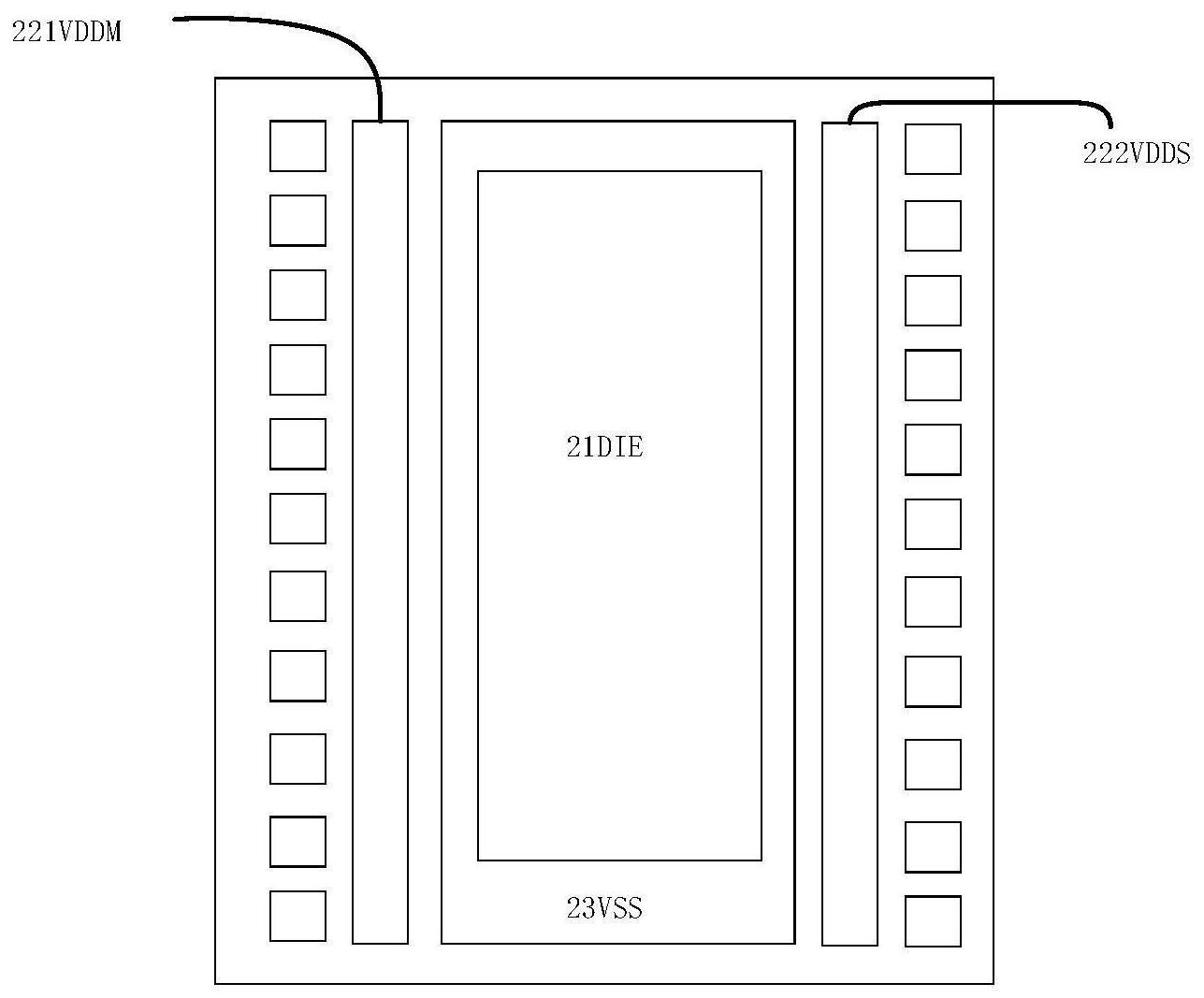

本发明实施例公开了一种芯片结构、封装方法以及电子设备,该芯片包括晶元(DIE)和电路基板,电路基板包括第一焊盘(VSS)、第二焊盘(VDDS)和第三焊盘(VDDM),其特征在于,所述晶元(DIE)布置在第一焊盘(VSS)上,晶元(DIE)在第一焊盘(VSS)的映射面在第一焊盘(VSS)边框内。相比于现有技术,在本发明实施例中,晶元(DIE)布置在第一焊盘(VSS)上,晶元(DIE)在第一焊盘(VSS)的映射面在第一焊盘(VSS)边框内,晶元(DIE)不会横跨2个或者多个Pad上,不会造成晶元(DIE)在封装过程中受力不均,因而不会产生芯片裂片损失,保证了芯片生产的良率。