授权公布号:CN112151452B

半导体结构及其形成方法

有效

申请

2019-06-28

申请公布

2020-12-29

授权

2024-03-26

预估到期

2039-06-28

| 申请号 | CN201910579446.7 |

| 申请日 | 2019-06-28 |

| 申请公布号 | CN112151452A |

| 申请公布日 | 2020-12-29 |

| 授权公布号 | CN112151452B |

| 授权公告日 | 2024-03-26 |

| 分类号 | H01L21/8238;H01L27/092;H10B10/00 |

| 分类 | 基本电气元件; |

| 申请人名称 | 中芯国际集成电路制造(上海)有限公司 |

| 申请人地址 | 上海市浦东新区中国(上海)自由贸易试验区张江路18号 |

专利法律状态

2024-03-26

授权

状态信息

授权

2020-12-29

公布

状态信息

公布

摘要

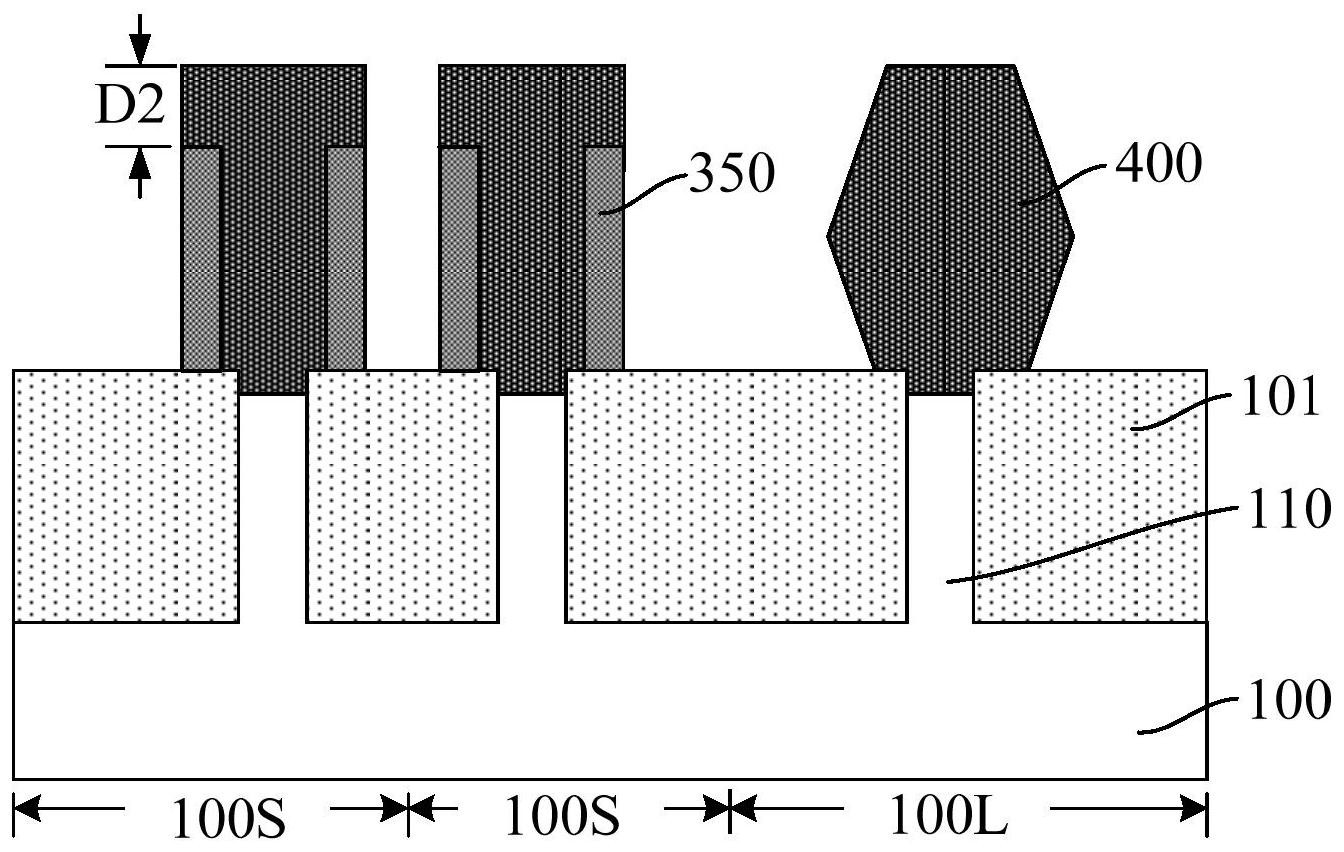

一种半导体结构及其形成方法,方法包括:提供基底,包括衬底和凸出于衬底的鳍部,衬底包括P型逻辑区和上拉晶体管区;形成横跨鳍部的栅极层;形成掩膜侧墙,覆盖上拉晶体管区中的鳍部侧壁、以及P型逻辑区中的部分鳍部侧壁;以掩膜侧墙为掩膜去除栅极层两侧的部分厚度鳍部,形成由逻辑区的鳍部和掩膜侧墙围成的凹槽、以及沿垂直于鳍部侧壁方向贯穿上拉晶体管区的鳍部和掩膜侧墙的通槽;在凹槽和通槽中形成P型源漏掺杂层。凹槽侧壁的掩膜侧墙限制P型源漏掺杂层过度生长,通槽使P型逻辑区的P型源漏掺杂层具有较大的宽度尺寸,从而减小对逻辑器件性能的影响、降低相邻上拉晶体管区的P型源漏掺杂层发生桥接的概率。