授权公布号:CN114078760B

半导体结构的及其形成方法

有效

申请

2020-08-14

申请公布

2022-02-22

授权

2024-03-22

预估到期

2040-08-14

| 申请号 | CN202010819887.2 |

| 申请日 | 2020-08-14 |

| 申请公布号 | CN114078760A |

| 申请公布日 | 2022-02-22 |

| 授权公布号 | CN114078760B |

| 授权公告日 | 2024-03-22 |

| 分类号 | H01L21/8234;H01L27/088 |

| 分类 | 基本电气元件; |

| 申请人名称 | 中芯国际集成电路制造(上海)有限公司 |

| 申请人地址 | 上海市浦东新区中国(上海)自由贸易试验区张江路18号 |

专利法律状态

2024-03-22

授权

状态信息

授权

2022-03-11

实质审查的生效

状态信息

实质审查的生效;IPC(主分类):H01L21/8234;申请日:20200814

2022-02-22

公布

状态信息

公布

摘要

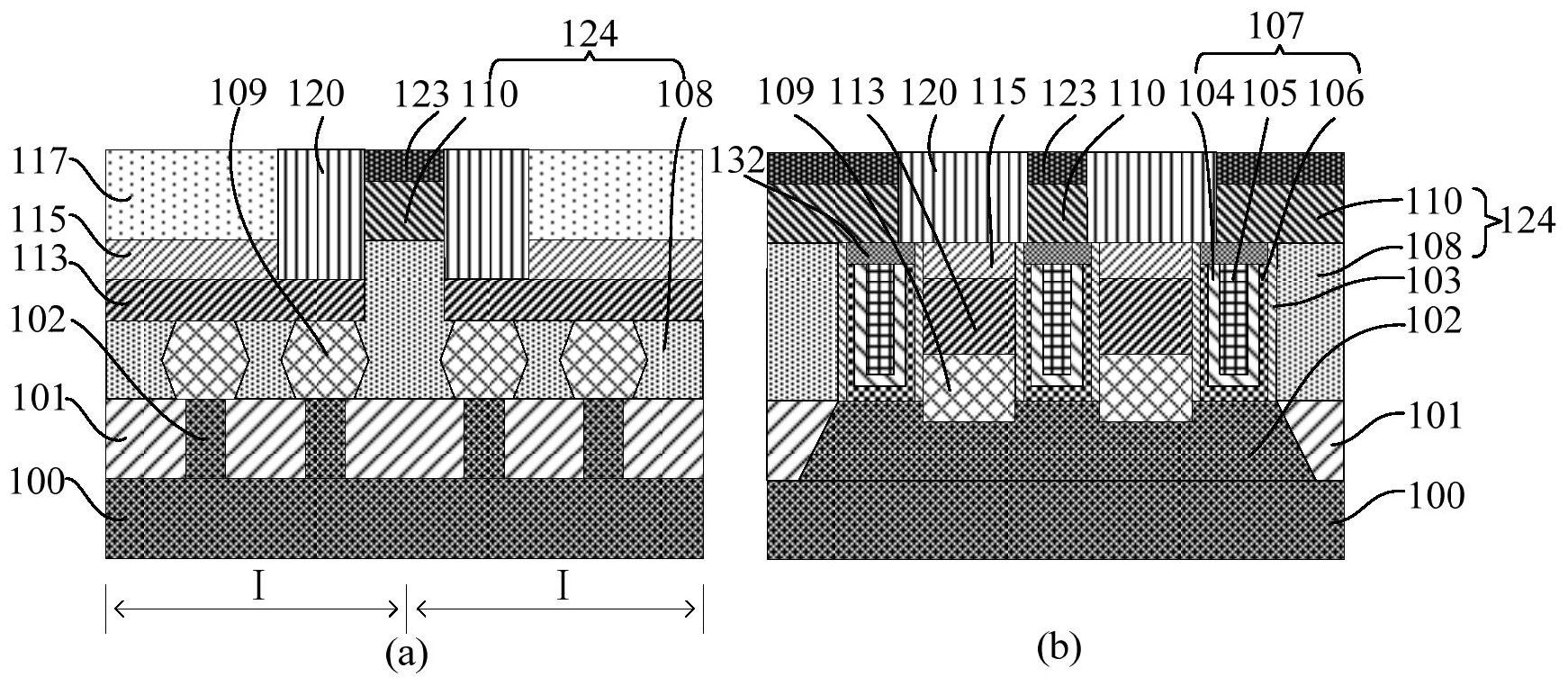

一种半导体结构及其形成方法,方法包括:提供基底,基底上有栅极结构,栅极结构两侧基底内有源漏掺杂层,基底上有第一介质层,覆盖栅极结构顶部,第一介质层顶部有硬掩膜材料层,基底包括多个相邻的器件单元区;刻蚀栅极结构两侧的硬掩膜材料层,保留器件单元区交界处和栅极结构上方的作为硬掩膜层;以硬掩膜层为掩膜刻蚀第一介质层,形成露出源漏掺杂层顶部的开口;在开口露出的源漏掺杂层顶部形成底部源漏插塞;在底部源漏插塞顶部形成第二介质层,覆盖硬掩膜层侧壁;形成贯穿第二介质层且与底部源漏插塞相接触的顶部源漏插塞,相邻器件单元区的顶部源漏插塞通过硬掩膜层相隔离。本发明通过硬掩膜层提高顶部源漏插塞与底部源漏插塞的对准精度。