授权公布号:CN112951720B

半导体结构的形成方法、半导体器件

有效

申请

2019-11-26

申请公布

2021-06-11

授权

2024-03-22

预估到期

2039-11-26

| 申请号 | CN201911174025.2 |

| 申请日 | 2019-11-26 |

| 申请公布号 | CN112951720A |

| 申请公布日 | 2021-06-11 |

| 授权公布号 | CN112951720B |

| 授权公告日 | 2024-03-22 |

| 分类号 | H01L21/3213;H01L21/311 |

| 分类 | 基本电气元件; |

| 申请人名称 | 中芯国际集成电路制造(上海)有限公司 |

| 申请人地址 | 上海市浦东新区中国(上海)自由贸易试验区张江路18号 |

专利法律状态

2024-03-22

授权

状态信息

授权

2021-07-02

实质审查的生效

状态信息

实质审查的生效;IPC(主分类):H01L21/3213;申请日:20191126

2021-06-11

公布

状态信息

公布

摘要

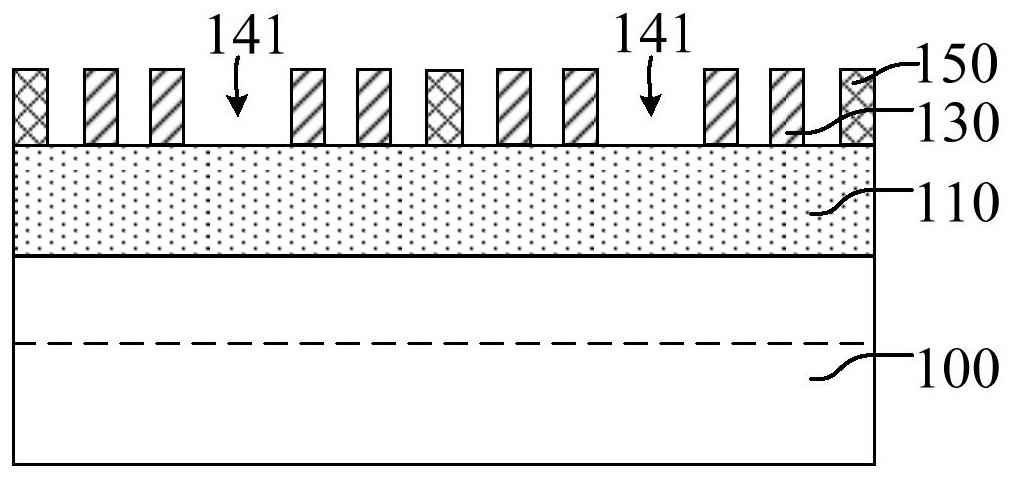

一种半导体结构的形成方法、半导体器件,形成方法包括:提供基底,基底上形成有待刻蚀层;在待刻蚀层上形成多个分立的核心层;在核心层的侧壁上形成第一侧墙,核心层与位于核心层侧壁上的第一侧墙构成一组图形单元,多组图形单元之间间隔排列;形成位于图形单元侧壁上的第二侧墙,相邻的第二侧墙与待刻蚀层围成凹槽;在凹槽中形成第三侧墙;去除核心层;去除第二侧墙,以第一侧墙和第三侧墙为掩膜,刻蚀待刻蚀层,形成目标图形。本发明实施例有利于防止相邻核心层之间的间距落入光刻工艺的禁止周期中,进而有利于降低形成核心层的光刻工艺的工艺难度、增大形成核心层的光刻工艺的工艺窗口,相应有利于提高目标图形的形成质量。