授权公布号:CN108023588B

基于FPGA的时钟恢复电路

有效

申请

2016-10-31

申请公布

2018-05-11

授权

2023-05-23

预估到期

2036-10-31

| 申请号 | CN201610932833.0 |

| 申请日 | 2016-10-31 |

| 申请公布号 | CN108023588A |

| 申请公布日 | 2018-05-11 |

| 授权公布号 | CN108023588B |

| 授权公告日 | 2023-05-23 |

| 分类号 | H03L7/08 |

| 分类 | 基本电子电路; |

| 申请人名称 | 研祥智能科技股份有限公司 |

| 申请人地址 | 广东省深圳市宝安区新安街道海滨社区宝兴路6号海纳百川总部大厦A座5层522 |

专利法律状态

2023-07-07

专利申请权、专利权的转移

状态信息

专利权的转移;IPC(主分类):H03L7/08;专利号:ZL2016109328330;登记生效日:20230627;变更事项:专利权人;变更前权利人:研祥智能科技股份有限公司;变更后权利人:深圳市亿万克数据设备科技有限公司;变更事项:地址;变更前权利人:518107 广东省深圳市光明新区高新路11号研祥智谷创祥地1号5楼;变更后权利人:518101 广东省深圳市宝安区新安街道海滨社区宝兴路6号海纳百川总部大厦A座5层522

2023-07-07

专利申请权、专利权的转移

状态信息

专利权的转移;IPC(主分类):H03L7/08;登记生效日:20230627;变更事项:专利权人;变更前:研祥智能科技股份有限公司;变更后:深圳市亿万克数据设备科技有限公司;变更事项:地址;变更前:518107 广东省深圳市光明新区高新路11号研祥智谷创祥地1号5楼;变更后:518101 广东省深圳市宝安区新安街道海滨社区宝兴路6号海纳百川总部大厦A座5层522

2023-05-23

授权

状态信息

授权

2019-09-27

实质审查的生效

状态信息

实质审查的生效;IPC(主分类):H03L7/08;申请日:20161031

2018-05-11

公布

状态信息

公布

摘要

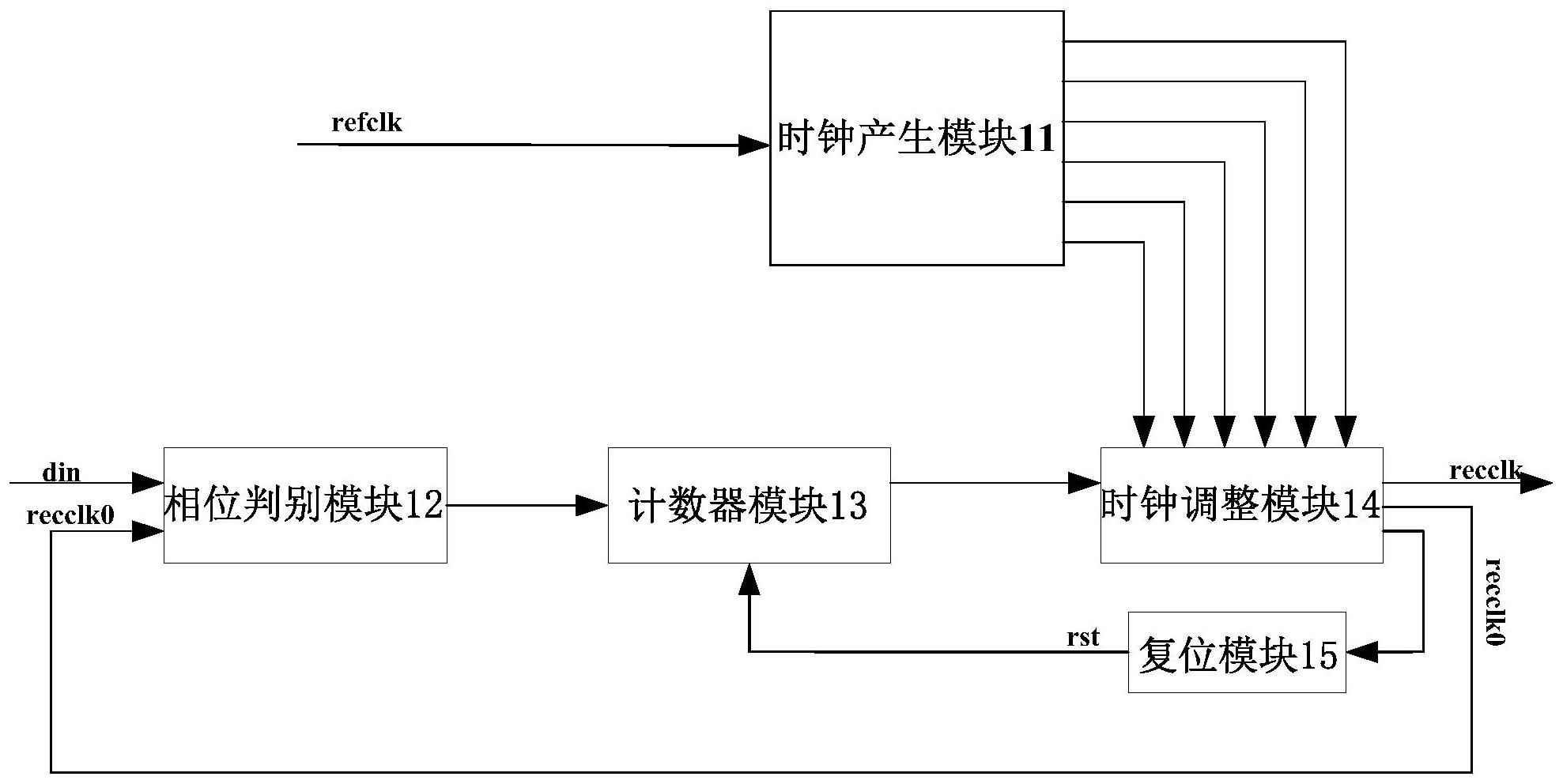

本发明提供一种基于FPGA的时钟恢复电路。所述基于FPGA的时钟恢复电路产生多个与输入数据频率相同、相位不同的参考时钟信号,对输入数据与所述锁相环产生的参考时钟信号的相位关系进行判别,根据相位关系判别结果是超前或者滞后的状态从而对时钟信号进行控制输出。本发明能够根据判别出的输入数据与参考时钟信号的超前或者滞后关系,经过切换不同相位的参考时钟信号,实现高速数据传输速率下时钟信号与输入数据的同步。