授权公布号:CN113194008B

基于FPGA的SV延时可测方法、装置、系统及存储介质

有效

申请

2021-04-27

申请公布

2021-07-30

授权

2023-02-28

预估到期

2041-04-27

| 申请号 | CN202110460305.0 |

| 申请日 | 2021-04-27 |

| 申请公布号 | CN113194008A |

| 申请公布日 | 2021-07-30 |

| 授权公布号 | CN113194008B |

| 授权公告日 | 2023-02-28 |

| 分类号 | H04L43/0852 |

| 分类 | 电通信技术; |

| 申请人名称 | 深圳市源拓光电技术有限公司 |

| 申请人地址 | 广东省深圳市宝安区石岩街道石龙社区森海诺科创大厦11F-12F |

专利法律状态

2023-02-28

授权

状态信息

授权

2021-07-30

公布

状态信息

公布

摘要

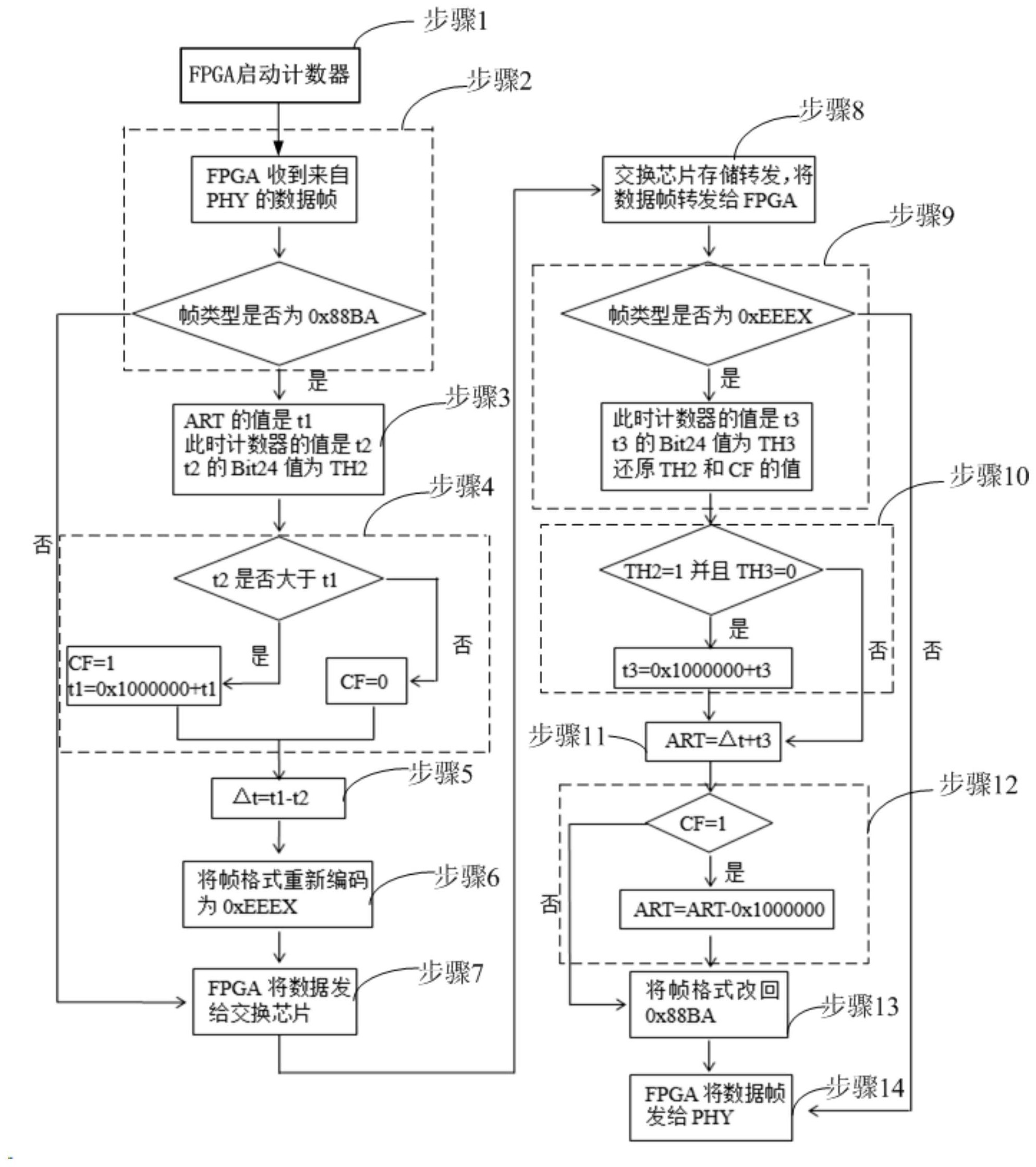

本发明提供了一种基于FPGA的SV延时可测方法、装置、系统及存储介质,该SV延时可测方法包括执行以下步骤:步骤1:上电后FPGA启动计数器;步骤2:FPGA接收来自PHY的数据帧,FPGA解析并判断该数据帧,如果以太网类型为0x88BA,则FPGA判定该数据帧为SV数据帧,并执行下一步骤,否则执行步骤7;步骤3:将步骤2判定的SV数据帧里面的交换延时累加值ART记为t1。本发明的有益效果是:本发明的SV延时可测方法将以太网帧类型的帧格式进行重新编码,选取了一个保留字段的帧类型进行编码,将两个标志位编码到帧类型里面,当数据帧离开交换机时,将数据帧重新编码恢复帧类型,保证了SV有24位的计数值。